Éditions Universitaires Européennes

Découvrez Notre Riche Collection Universitaire

De la Recherche Innovante aux Ouvrages de Référence

Nous avons à cœur de vous proposer un vaste choix d’ouvrages universitaires dans de multiples domaines. De la sociologie à la physique quantique, en passant par l’histoire de l’art et l’économie, notre catalogue illustre toute la richesse et la diversité de la recherche universitaire actuelle.

Que vous soyez étudiant, chercheur ou simplement curieux, vous trouverez sans aucun doute des titres qui éveilleront votre intérêt et enrichiront vos connaissances.

L'édition de livre pour tous vos travaux de recherche

Notre service d’édition de livres vous permet de transformer vos travaux de recherche en publications professionnelles.

Nous nous engageons dans l’édition de livre pour publier une vaste gamme de travaux universitaires de haute qualité. Notre catalogue diversifié comprend des recherches novatrices, des actes de conférence stimulants, des manuels pédagogiques de référence, des mémoires de fin d’études éclairants, ainsi que des thèses doctorales à la pointe de leur domaine.

En choisissant notre maison d’édition pour l’édition de votre livre, vous contribuez à l’avancement des connaissances et partagez vos précieux travaux avec la communauté scientifique internationale. Ensemble, faisons progresser le savoir académique à travers l’édition de livres de qualité.

VOTRE ASSISTANT VIRTUEL

Des réponses instantanées à toutes vos questions sur la publication

Vous avez des questions sur le processus de publication ?

Notre assistant virtuel intelligent est là pour vous aider 24h/24, 7j/7.

Que vous ayez besoin d’éclaircissements sur la soumission de manuscrits, le formatage, les droits d’auteur ou tout autre aspect de la publication, notre chatbot IA est prêt à vous fournir des réponses rapides et précises.

Commencez une conversation et obtenez l’aide dont vous avez besoin pour transformer votre ouvrage en un livre publié.

Diffusion

Internationale

Nous diffusons votre livre dans plus de 40 pays à travers les libraires les plus reconnus.

Assistance

personnalisée

Notre équipe est là pour vous aider avec dévouement durant le processus de publication.

Technologie

d’impression écologique

L’impression à la demande est une technique innovatrice d’impression rapide, efficace et respectueuse de l'environnement.

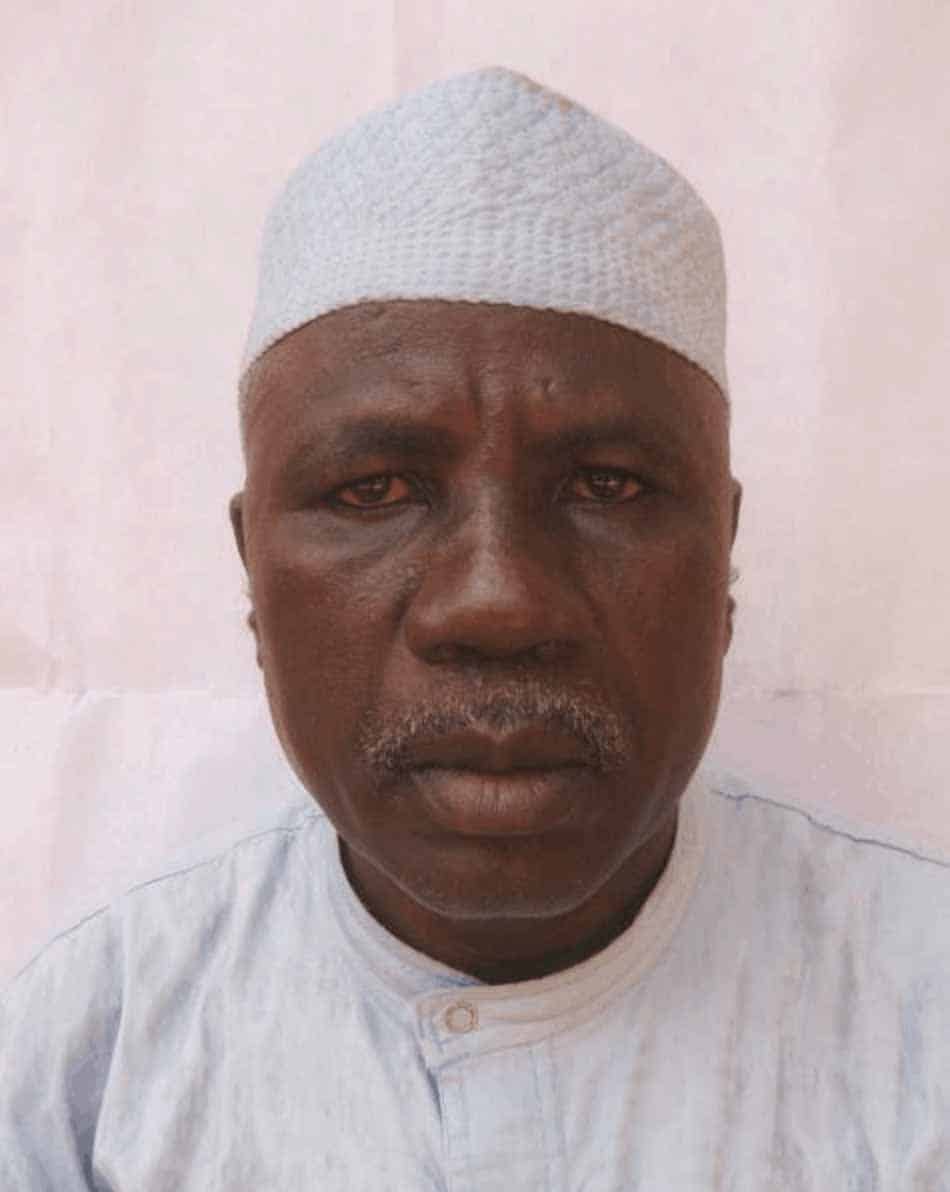

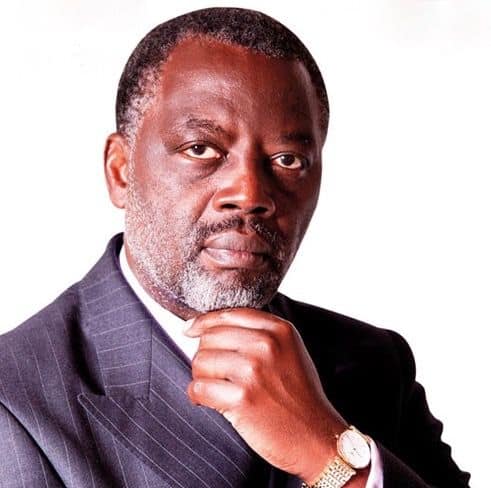

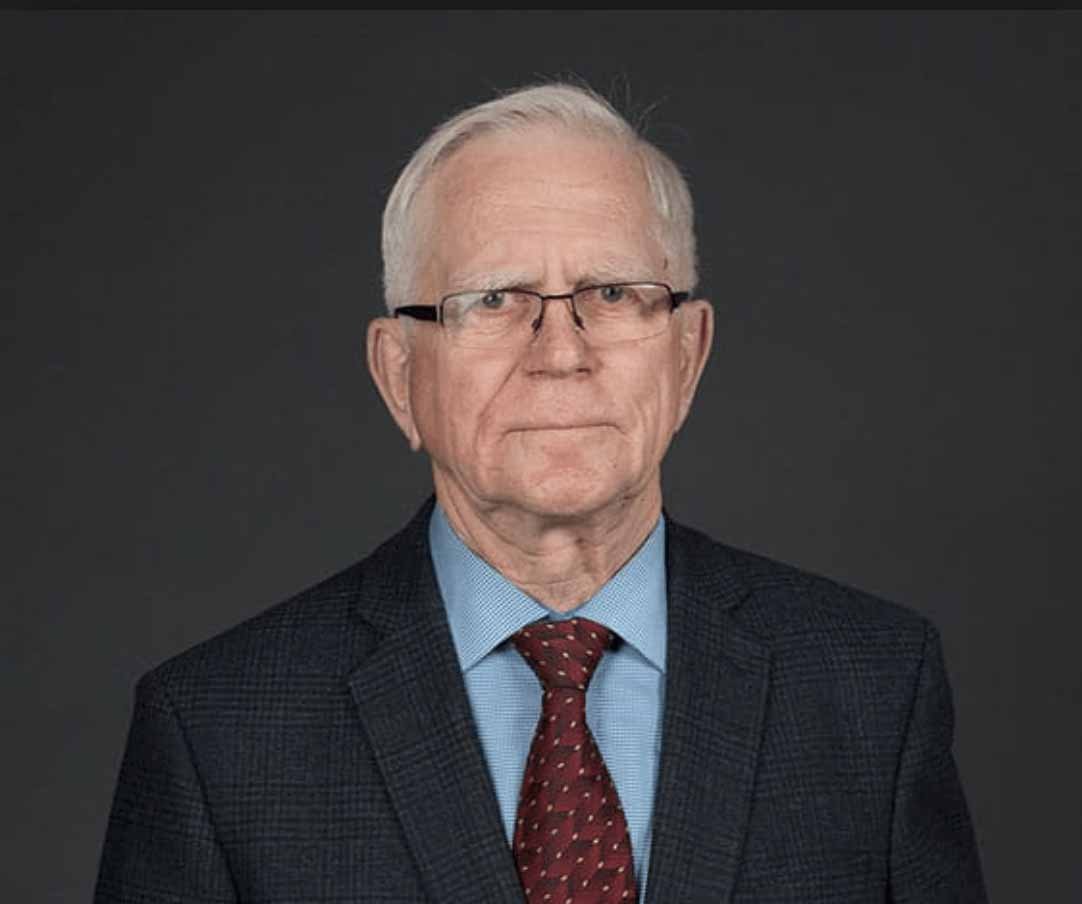

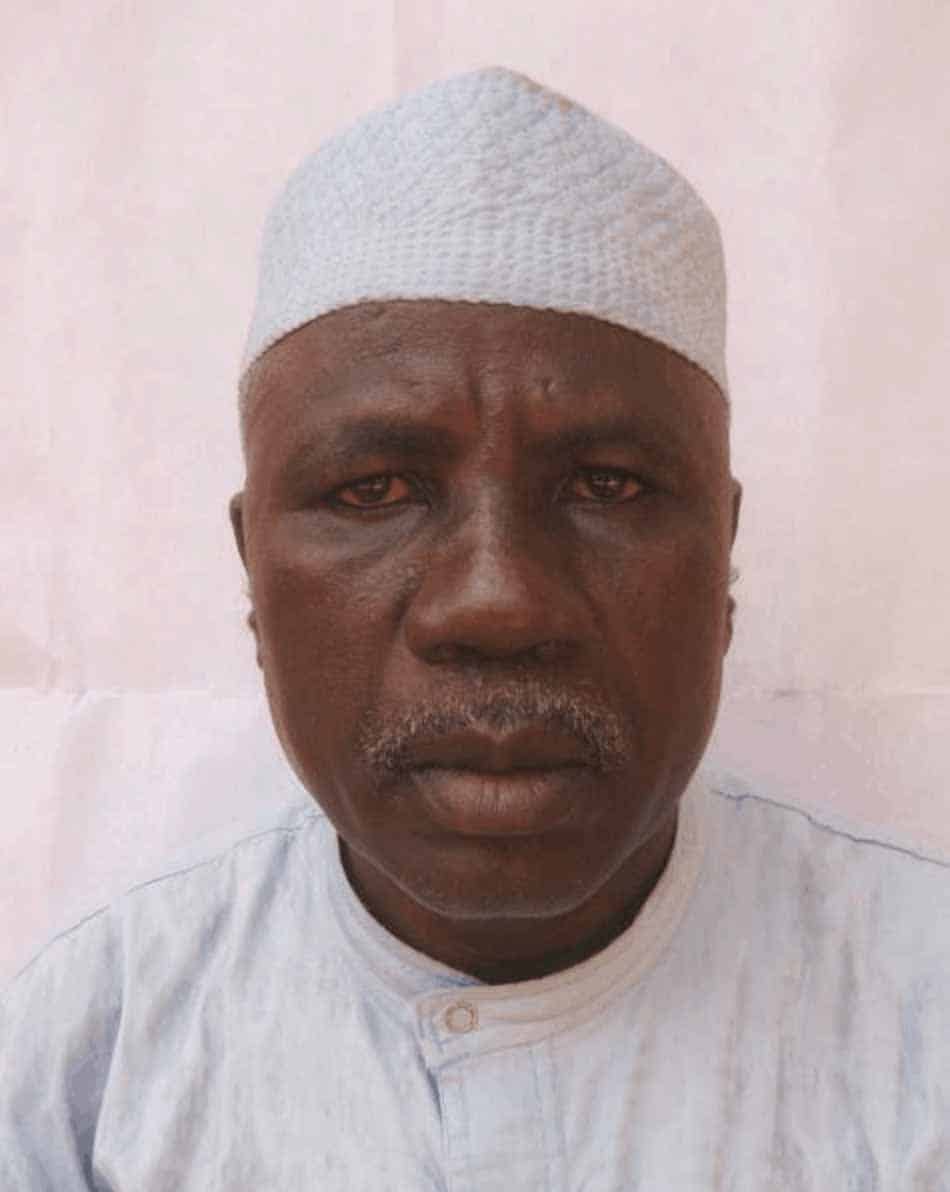

Ce que disent nos auteurs

Par où commencer?

-

Soumettez nous votre proposition de livre

Faites nous parvenir votre ouvrage ou tout simplement un résumé.

-

Un contrat d'édition vous sera offert

L'acceptation de votre ouvrage est suivie d'un contrat d'édition qui vous sera proposé.

-

Façonnez votre livre sur notre plateforme

Laissez libre cours à votre créativité pour donner forme à votre livre.

-

Commandez vos exemplaires imprimés

Bénéficiez de réductions sur les exemplaires imprimés de votre livre.

Plus de100,000fans facebook

Votre livre, dans le monde entier!

Notre réseau de diffusion s’étend bien au dèla des frontières de la France. Nous collaborons avec des diffuseurs internationaux tels que Amazon ou encore Hachette Distribution pour desservir tous les marchés francophones. Nous vous garantissons une commercialisation ininterrompue et internationale de votre livre.

Morebooks - Notre boutique affiliée

Le groupe OmniScriptum possède sa propre boutique affiliée. Grâce à MoreBooks !, nos auteurs et nos distributeurs peuvent bénéficier de rabais spéciaux, d’offres et d’options d’expédition partout dans le monde. MoreBooks ! n’a pas de frontières, nous livrons dans le monde entier !

Nous avons beaucoup plus de distributeurs dans le monde entier.

Cliquez ici pour voir la liste complète des distributeurs.

Australie

- ALS Library Services Pty Ltd

- Lightning Source Australia

Belarus

- Chebakov.com

- IP Gnedko Nikolay Grigorevich

Bolivie

- Editorial Master Bolivia

- Sr.Libro de Hugo Richard Villanueva Lungasso

- Acchini Libros

- Libreria Medica Galenos

Bosnie Herzégovine

- Books.ba d.o.o.

Brésil

- Livraria Canuto

- De Olho no Livro Distribuidora Ltda

- Distribuidora Ltda

- Octopos Comercio e servicos Ltda me

- Livraria Multi SJ Campos

- SBS – Special book services

- Livraria Pandora

- M.A. Pontes Editora e Distribuidora de Livros Ltda.

- Freebook Comercio de Livros e Revistas Ltda.

- Susanne Bach Comercio de Livros Ltda.

Bulgarie

- Index Ltd

- Level Up

Canada

- Hachette Livre International

Chili

- Miguel Concha S.A.

- Duran San Martin Cia Ltda.

- Juan Eduardo Troncoso Medina

Chine

- China Educational Publications Import & Export Corporation CEPC

- China Educational Publications Import & Export Corporation HEBF

- ARBERT INT’L BOOK CO., LTD

- Beijing Publications Import & Export Corporation Ltd. BPIEC

- Beijing ZhongKe I/E Company

- China Book Import Center

- China National Publication Import & Export Corporation Shanghai CNPIECS

- China National Publications Import & Export Corporation Guanezhou Branch

- China National Publication Import & Export Corporation CNPIECS

- China National Sci-Tech Information IMP.&EXP.

Corporation - China Publishers Services

- Unifacmanu

- Bookone Cultural Books Co.

- Chinmu Village Co., Ltd.

Colombie

- Ediciones EuroAmerica S.A.S

- Ediciones Modernas Ltda.

- Ediciones de la U

- El Bibliotecologo

- EUROLIBROS Ltda.

- Promolibro

- Distribooks

- Mundo XXI Ediciones

- INGLOBATEC S.A.S.

Croatie

- Robert’s Plus d.o.o.

République Tchèque

- SUWECO CZ, spol. s.r.o.

- Bohemian Ventures spol. s.r.o.

- Megabooks CZ spol. s.r.o.

- Intes

Equateur

- Importext

- Ediciones Valladolid

- Libros & Libros

Egypte

- Dar Al Fajr

- The Middle East Readers Information Center

France

- Amazon.fr

- Fnac.fr

- AMALIVRE

- TALION DIFFUSION SERVICES

- LE NOUVEAU PONT

- DawsonFrance

- Librairie Dalloz

- Le Monde en Tique

- SIDE (Société Internationale de Diffusion et d’Edition)

- Kitab-Liaison

- Centre d’Exportation du Livre

- Librairie S.D.D

- Librairie Mollat

- Hachette Distribution

Géorgie

- Santa Esperanza LTD.

Allemagne

- amazon.de

- Koch, Neff & Volckmar GmbH (KNV)

- Libri GmbH

- G. Umbreit GmbH & Co. KG

Hongrie

- Book Station

- Ronni Kereskedelmi és Kulturális Szolgáltató Bt.

Inde

- Researchco Book Centre

- Sarat Book House Pvt. Ltd.

- Shah Book House Pvt. Ltd.

- Universal Book Shop

Indonesie

- Putra Standards Pte. Ltd

- CV Fenross Corporation

Iran

- Vijehnashr Int Books & Journal Services

Italie

- Libreria Cortina Torino

- DAN Europe

- Media Web di Allegra Gaetano

Côte d’Ivoire

- Accolade Diffussion

Jordanie

- Jordan Book Centre

Kazakhstan

- Logobook.kz

Kenya

- Educate Yourself Ltd

Corée du Sud

- DAEJUNG TRADING COMPANY

- Dasansogo Ltd.

- Haksul Intelligence Co. Ltd.

- Kyobo Book Centre Ltd.

- Pan Korea Book Corp

- Yeil Books

- YOO REE Information Co.

- Gisik Jungbo Co.

- IBA Korea

Liban

- Librairie Antoine S.A.L.

Lithuanie

- UAB “ir Knygos”

Malaysie

- Innowawasan Sdn. Bhd

- Global Books Frontier Sdn Bhd

Mexique

- Sistemas Biblioinforma

- LSR Libros

- Libros Libros SA de CV

- Book Dealer Co. de México

- Probooks

- Ediciones Nanobooks

- Libros Cinco Continentes S.A. de C.V.

- Libreria Bonilla y Asociados SA De CV

- EDUCARB SA DE CV

Maroc

- Librairie Papeterie Nationale

Pays-Bays

- INDEX Books

- Academic Book Import

Nigéria

- Jasper Books

Maghreb & Dom-Tom

- Réseau Hachette Livre International

Pakistan

- ALLIED BOOK COMPANY

- Progressive International Agencies Pvt Ltd

- Multi-Line Books

- Iqra Book Agency

Peru

- Libreria Cientifica y Tecnologica Universitaria SAC

Philippines

- MegaTEXTS Phil., Inc.

Pologne

- ABE-IPS Sp.z o.o.

- Afiliant P. Szalamacha i Wspolnicy sp.j. / Albertus.pl

- Press Import Wydawnictv Naukowych sp.j.

Portugal

- Livraria Ferin

- Livraria Bokspot

Roumanie

- Prems Librexim SRL

- Callisto Comexim srl

- PRIOR MEDIA GROUP

- Romdidac

Russie

- Logosphera / Logobook.ru

- Internet Prodazhi / Setbook.net

- IC Yagello Oleg Yurievich

- Planeta Alians LLC

- Ozon

- ITD Perspektiva

- MK-Periodika

- KONEK

- Bookhunter Ltd

- Eposervis

- Relod

- Infra Inzheneria

- Jupiter-Impex

- Medlennie Knigi

- Permkniga

Arabie Saoudite

- Al Shegrey KSA

Singapore

- UBS Library Services Pte Ltd

- Alkem Company

- Putra Standards Pte. Ltd

Slovakie

- Male Centrum Ltd.

- Slovart G.T.G. GmbH

Afrique du Sud

- Vuga Books

Espagne

- Libreria Bosch

- Los Andes Libros S.L.

- Libreria Central Librera Ferrol S.L.

- Ascra Distribucions, S.L.

- Libreria Agricola de Jerez S.L.

- Binario Libros S.L.

- AXÓN Librería

- Libreria Herrero S.A.

- Llibreria Ali I Truc, S.L.

- Puvill Libros S.A.

- Libreria Medica Murciana

- Libreria Pons SL

- Libreria BioGea

- Libreria Grafos

- Dawson España

- Latina Libros

- Cauce Libros

- La Panoplia Export S.L.

- BuscaLibre España S.L.

Suisse

- Unique-Publishing

Taiwan

- ARBERT INT’L BOOK CO., LTD.

- China Publishers Services

- GreenPo Books

- Knowledge Book Co.

- Unifacmanu

- Bookone Cultural Books Co.

- Chinmu Village Co., Ltd.

Tunisie

- Réseau Hachette Livre Diffusion

Turquie

- Caglayan Kitabevi-Tuncay Caglayan

- Palme Publications and Bookstores

- Asrin Bookstore Distribution and Marketing Limited Company

- AC Bookstore

- TEMPO YAYIN

Uruguay

- Renart Libros Srl

Emirats Arabes Unies

- University Book House

Grande Bretagne

- Amazon

- Bertram Trading Ltd

- Lambrick Enterprises

- Book Depository

- Mallory International Ltd (mainly for African market)

- Archidemia

- CBL Distribution Ltd

Etats Unis

- Cranbury International LLC

- Complete Book & Media Supply

- Reiter’s Books

Viêt-Nam

- Cultural Development Import and Export Co. (CDIMEX)

Auteurs récemment publiés